メモリ(全77問中44問目)

No.44解説へ

メモリインターリーブの説明として,適切なものはどれか。

出典:平成21年秋期 問10

- CPUから主記憶へのアクセスを高速化するために,キャッシュメモリと主記憶との両方に同時にデータを書き込む。

- CPUから主記憶へのアクセスを高速化するために,主記憶内部を複数のバンクに分割し,各バンクを並列にアクセスする。

- CPUと主記憶のアクセス速度の違いによるボトルネックを解消するために,高速かつ小容量のメモリを配置する。

- パイプライン処理を乱す要因をなくすために,キャッシュメモリを命令用とデータ用の二つに分離する。

広告

解説

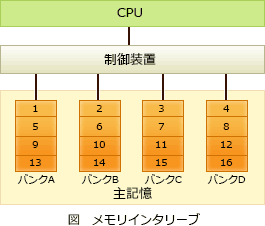

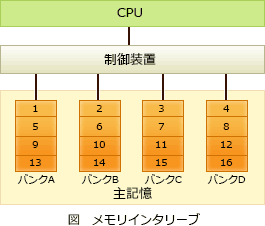

メモリインターリーブは、物理上はひとつである主記憶領域を、同時アクセス可能な複数の論理的な領域(バンク)に分け、それぞれのバンクに対してデータの読み書きを並列で行うことにより、メモリアクセスの高速化を図る技術です。メモリインターリーブでは、奇数アドレスはバンク1、偶数アドレスはバンク2というように、連続したアドレスを複数のバンクに割り振っていきます。通常は、連続するアドレスに次々とアクセスされることが多いため、見かけ上並列アクセスしているようになり、実効アクセス時間が短くなります。「主記憶に並列アクセス」ときたらメモリインターリーブです。

- 主記憶とキャッシュメモリの同期方法のひとつであるライトスルー方式の説明です。

- 正しい。メモリインターリーブの説明です。

- キャッシュメモリの説明です。

- パイプラインキャッシュメモリの更新回路の説明です。キャッシュミスヒット時に、データの更新処理と、後続のスレッドからのアクセス処理との競合を回避し、パイプライン動作の乱れを防止する効果があります。

広告