HOME»基本情報技術者平成13年春期»午前問22

基本情報技術者平成13年春期 午前問22

問22

主記憶装置の高速化の技法として,主記憶を幾つかのアクセス単位に分割し,各アクセス単位をできるだけ並行動作させることによって,実効的なアクセス時間を短縮する方法を何というか。

- 仮想記憶

- パイプライン

- マイクロプログラム

- メモリインターリーブ

- [出題歴]

- 基本情報技術者 H20秋期 問20

- ソフトウェア開発技術者 H17春期 問19

分類

テクノロジ系 » コンピュータ構成要素 » メモリ

正解

エ

解説

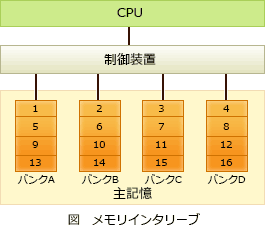

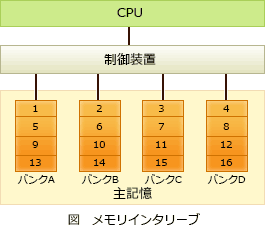

メモリインターリーブは、物理上はひとつである主記憶領域を、同時アクセス可能な複数の論理的な領域(バンク)に分け、それぞれのバンクに対してデータの読み書きを並列で行うことにより、メモリアクセスの高速化を図る技術です。メモリインターリーブでは、奇数アドレスはバンク1、偶数アドレスはバンク2というように、連続したアドレスを複数のバンクに割り振っていきます。通常は、連続するアドレスに次々とアクセスされることが多いため、見かけ上並列アクセスしているようになり、実効アクセス時間が短くなります。「主記憶に並列アクセス」ときたらメモリインターリーブです。

- 仮想記憶は、補助記憶装置(HDDなど)を仮想アドレス空間として使用することで、主記憶のサイズよりも大きなプログラムを実行可能にする方式です。

- パイプラインは、1つの命令をステージと呼ばれる複数の段階に分割して並列実行することで高速化を図る方式です。

- マイクロプログラムは、CPUの内部に組み込まれてCPUの動作を制御するためのプログラムです。

- 正しい。メモリインターリーブは、メモリ領域を複数のバンクに分けて並列アクセスすることで、実効アクセス時間の短縮を図る技法です。