HOME»基本情報技術者令和元年秋期»午前問21

基本情報技術者令和元年秋期 午前問21

問21

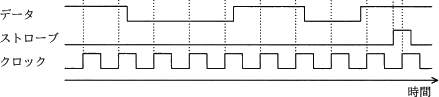

クロックの立上りエッジで,8ビットのシリアル入力パラレル出力シフトレジスタの内容を上位方向ヘシフトすると同時に正論理のデータをレジスタの最下位ビットに取り込む。また,ストローブの立上りエッジで値を確定する。各信号の波形を観測した結果が図のとおりであるとき,確定後のシフトレジスタの値はどれか。ここで,数値は16進数で表記している。

- 63

- 8D

- B1

- C6

- [出題歴]

- 応用情報技術者 H26春期 問22

- 応用情報技術者 H30春期 問22

分類

テクノロジ系 » ハードウェア » ハードウェア

正解

イ

解説

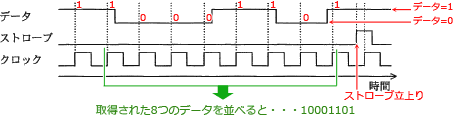

設問の図に、クロックの立上りエッジで取り込まれるビット(0 or 1)を書き込むと次のようになります。 データは取り込まれるごとに上位ビットにシフトされていくので、シフトレジスタのビットの並びは、ストローブの立上り直前に取得されたデータが最下位ビット、その1つ前のデータが最下位から数えて2ビット目…というようになっています。

データは取り込まれるごとに上位ビットにシフトされていくので、シフトレジスタのビットの並びは、ストローブの立上り直前に取得されたデータが最下位ビット、その1つ前のデータが最下位から数えて2ビット目…というようになっています。

ストローブ立上り前の8回分の取得ビットを並べると「10001101」ですので、これを16進数に変換した8Dが確定後のシフトレジスタの値となります。

ストローブ立上り前の8回分の取得ビットを並べると「10001101」ですので、これを16進数に変換した8Dが確定後のシフトレジスタの値となります。